名称:出租车计费系统设计Verilog代码modelsim仿真

软件:modelsim

语言:Verilog

代码功能:

出租车计费系统设计

设计一个出租车计费系统实现以下功能

(1)能实现计费功能,计费标准为:按行驶路程收费,起步费为7元,并在车行驶3公里后按每公里2元计费,当总费用达到或超过45元时,每公里按4元收费。当遇到红绿灯或其他情况需要停车等待时,则按时间计费,计费单价为每20s收费1元。

(2)系统预置功能:能预置起步费、每公里收费、车行加费里程、计时收费

(3)能模拟汽车行驶、停止、暂停等状态

(4)最后将路程与车费显示出来

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

1.要求

2.程序文件

3.程序运行

4.testbench

5.仿真图

1.起步价7元

2.speed 等于10,11时计费,

车行驶 3 公里后按每公里 2 元计费

总费用达到或超过 45 元时,每公里按 4 元收费

3.speed 等于11,01时计费

3.speed 等于00,01时计费

要停车等待时,则按时间计费,计费单价为每 20s 收费 1 元

停车结束计费

整体仿真图

部分代码展示:

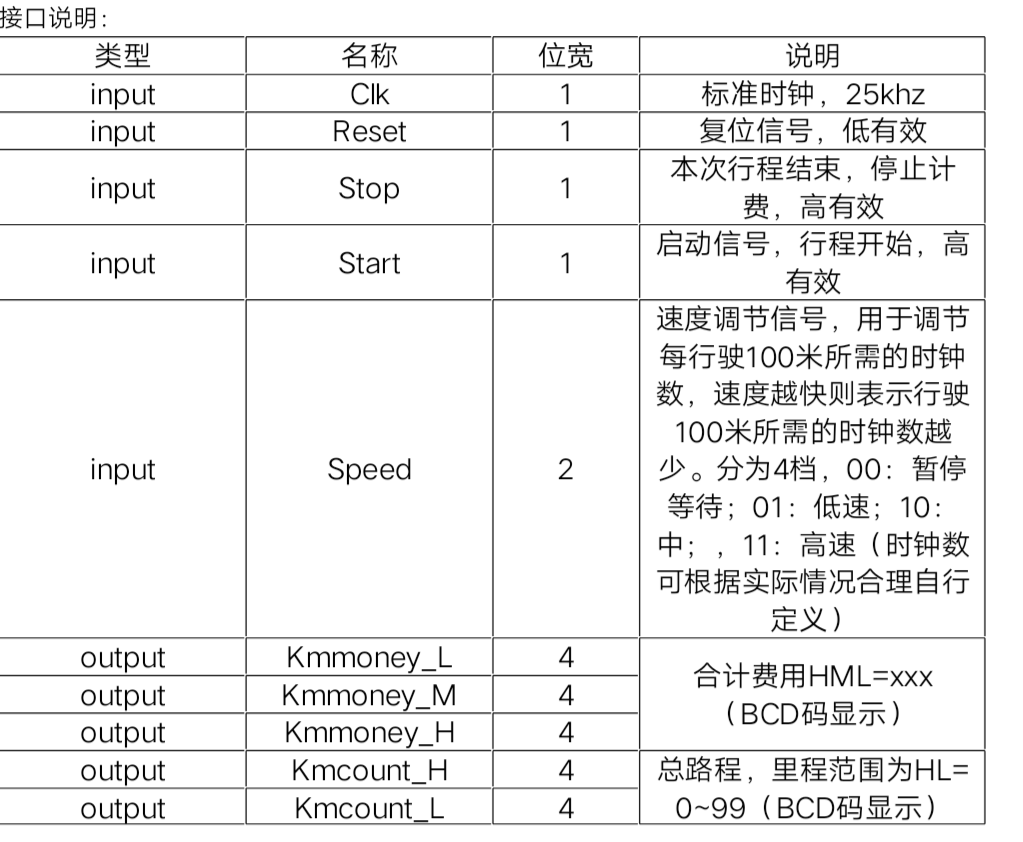

module?taxi_top( input?Clk,//标准时钟,25khz? input?Reset,//复位信号,低有效? input?Stop,//本次行程结束,停止计费,高有效 input?Start,//启动信号,行程开始,高有效? input?[1:0]?Speed,//00--暂停等待;01--低速;10--中;,11--高速 output?[3:0]?Kmmoney_L,//合计费用?BCD码显示 output?[3:0]?Kmmoney_M,//合计费用?BCD码显示 output?[3:0]?Kmmoney_H,//合计费用?BCD码显示 output?[3:0]?Kmcount_H,//总路程,BCD码显示 output?[3:0]?Kmcount_L//总路程,BCD码显示 ); wire?speed_pulse; wire?valid_1Hz; wire?wait_20seconds; wire?one_Km_pluse; //根据Speed,产生不同频率的速度脉冲 speed_pulse_ctrl?i_speed_pulse_ctrl( .?Clk(Clk),//25khz? .?Reset(Reset),//复位低有效? .?Speed(Speed),//00:暂停等待;01:低速;10:中;,11:高速 .?valid_1Hz(valid_1Hz),?//分频到1Hz .?speed_pulse(speed_pulse)?//速度档位 ); //20s产生一次,用于等待时计费 wait_for_20seconds?i_wait_for_20seconds( .?Clk(Clk),//25khz? .?Reset(Reset),//复位低有效? .?Speed(Speed),//00:暂停等待;01:低速;10:中;,11:高速 .?valid_1Hz(valid_1Hz),//1HZ .?wait_20seconds(wait_20seconds)?//等待20s产生一次脉冲 ); //1公里产生一次脉冲,用于里程计费 kilometre_pluse?i_kilometre_pluse( .?Clk(Clk),//25khz? .?Reset(Reset),//复位低有效? .?speed_pulse(speed_pulse), .

点击链接获取代码文件:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=1126

芯耀

芯耀

488

488